# Аппаратное обеспечение вычислительных, телекоммуникационных и управляющих систем

DOI: 10.18721/JCSTCS.11408

УДК 004

### РАЗРАБОТКА АППАРАТНО-РЕКОНФИГУРИРУЕМОГО ВЫЧИСЛИТЕЛЯ С ПОДДЕРЖКОЙ СТАНДАРТА OPENCL

А.П. Антонов, А.С. Филиппов, И.О. Киселев

Санкт-Петербургский политехнический университет Петра Великого, Санкт-Петербург, Российская Федерация

Наиболее важными параметрами современных суперкомпьютерных систем становятся отношение производительности к энергопотреблению и эффективная производительность (отношение реальной производительности к пиковой производительности). Аппаратно-реконфигурируемые вычислители, обеспечивая на аппаратном уровне возможность перестраивать структуру вычислителя под решаемую задачу, способны повысить эффективность суперкомпьютерных систем в соответствии с указанными параметрами. Аппаратно-реконфигурируемые вычислители предполагают использование современной элементной базы, средств высокоуровневого синтеза и соответствующих средств разработки. Существующие на рынке аппаратнореконфигурируемые вычислители позволяют строить высокопроизводительные гетерогенные суперкомпьютерные системы. В то же время для подготовки специалистов требуется массовое использование подобных платформ в учебных лабораториях, что необходимость разработки бюджетного варианта реконфигурируемого вычислителя, имеющего полную поддержку со стороны современных средств проектирования. В статье показана необходимость создания подобной платформы, приведены параметры и особенности разработанного на базе программируемой логики фирмы Xilinx вычислителя, имеющего полную совместимость со стандартом OpenCL и интегрированного в среду разработки SDAccel.

**Ключевые слова:** реконфигурируемые вычислительные системы, высокопроизводительные вычисления, ПЛИС, OpenCL, высокоуровневый синтез аппаратуры, образовательные технологии.

Ссылка при цитировании: Антонов А.П., Филиппов А.С., Киселев И.О. Разработка аппаратно реконфигурируемого вычислителя с поддержкой стандарта OpenCL // Научно-технические ведомости СПбГПУ. Информатика. Телекоммуникации. Управление. 2018. Т. 11. № 4. С. 108—118. DOI: 10.18721/JCSTCS.11408.

## DESIGN OF RECONFIGURABLE COMPUTER SUPPORTING OPENCL STANDARD

A.P. Antonov, A.S. Filippov, I.O. Kiselev

Peter the Great St. Petersburg Polytechnic University, St. Petersburg, Russian Federation

The most significant parameters of modern supercomputing systems are performance to power consumption rate and effectiveness (real performance to peak performance rate). Hardware-reconfigurable computers can provide real-time hardware adaptation according

to the specific task, improving the given parameters. Reconfigurable computing uses cutting-edge hardware and high level synthesis tools for parallel computations. For this reason, skilled engineers are required for managing such systems. The existing reconfigurable high-performance computing modules allow building heterogeneous supercomputer systems. However, they are too expensive and unsuitable for education purposes. In this paper, we have confirmed the need for cheap reconfigurable computers that could be used as educational facilities for students and described the significant features of the designed OpenCL-compatible reconfigurable platform.

**Keywords:** reconfigurable computers, high-performance computing, FPGA, OpenCL, high-level synthesis, educational technologies.

Citation: Antonov A.P., Filippov A.S., Kiselev I.O. Design of reconfigurable computer supporting OpenCL standard. St. Petersburg State Polytechnical University Journal. Computer Science. Telecommunications and Control Systems, 2018, Vol. 11, No. 4, Pp. 108–118. DOI: 10.18721/JCSTCS.

Введение. В настоящее время мир высокопроизводительных вычислений базируется на гибридных вычислительных системах, в которых кроме массивов процессоров общего назначения различной структурной организации имеются специализированные вычислительные узлы SIMD (Single Instruction Multiple Data), реализованные на базе технологии CUDA. Однако энергоэффективность и эффективная производительность таких систем чувствительна к структурной организации алгоритмов решаемых задач: ее соответствию архитектуре суперкомпьютерной системы [1].

Современным подходом к увеличению энергоэффективности и эффективной производительности суперкомпьютерных систем является реализация гетерогенных систем, предполагающих использование аппаратно-реконфигурируемых вычислителей, аппаратная структура которых в режиме реального времени подстраивается под структурную организацию алгоритмов решаемых задач [2]. Основа для реализации аппаратно-реконфигурируемых вычислителей — современные СБИС Программируемой Логики (FPGA), выпускаемые компаниями Intel [3] и Xilinx [4].

Задачи создания аппаратуры мультипроцессорных систем и CUDA-ускорителей решены: подобные изделия выпускаются серийно. Аппаратно-реконфигурируемые вычислители — новый и активно развивающийся класс вычислительных устройств. Разработка аппаратуры и интеграция подобного вычислителя в гетерогенную вычислительную систему является нетривиальной задачей, т. к. требует использования современных FPGA и специального программного обеспечения. Кроме того, для создания, внедрения и эксплуатации подобных систем требуются подготовленные инженеры. Из этого следует, что для развития отрасли высокопроизводительных вычислений актуальны задачи создания реконфигурируемых вычислительных комплексов, учебных лабораторий и соответствующих курсов обучения.

Стандарт OpenCL. Для создания специализированных вычислительных устройств чаще всего используют FPGA. При этом для того, чтобы реализовать требуемый алгоритм на базе FPGA и создать конфигурационный файл требовалось использовать языки описания аппаратуры и вручную переходить от описания алгоритма на языках высокого уровня к языку описания аппаратуры. Такой переход требует от инженера знания всех особенностей аппаратной платформы, языка высокого уровня (например С++ или MATLAB) и предметной области реализуемой задачи.

По этой причине, несмотря на удачные примеры применения FPGA в области суперкомпьютерных вычислений, широкого распространения реконфигурируемые вычислители не получили [6]. Для упрощения процесса проектирования и формализации процесса перехода от алгоритмической симуляции к аппаратной реализации появились средства высокоуровневого синтеза аппаратуры, т. е. преобразование текста программы, написанного на языках высокого уровня, в

язык описания аппаратуры. В настоящее время подобные средства предоставляются производителями FPGA: Xilinx и Intel.

Попытки создания средств высокоуровневого синтеза, т. е. программного обеспечения, которое в автоматизированном режиме преобразует алгоритм, описанный на языках высокого уровня абстракции, в описание на языках описания аппаратуры, которое было бы функционально тождественным исходному алгоритму, предпринимались неоднократно, некоторые из них были весьма успешными [7]. В России также ведутся разработки собственных методик высокоуровневого синтеза. В [8] описан специализированный язык высокого уровня для разработки реконфигурируемых вычислительных систем — COLAMO.

Долгое время подобные проекты не поддерживались производителями FPGA. Однако ситуация изменилась с появлением стандарта OpenCL — кроссплатформенным расширением языка C++, позволяющим писать однотипный код для выполнения параллельных вычислений для различного типа платформ (CPU, GPU, FPGA). OpenCL активно используется при разработке программного обеспечения для суперкомпьютеров и систем обработки больших данных и позволяет, не внося значительных изменений в описание алгоритма, быстро заменить один тип вычислителя на другой [9, 10].

В [11] показано, что использование методов высокоуровневого синтеза позволяет сократить время разработки, тестирования и интеграции платформы на основе FPGA в гетерогенную вычислительную систему до шести раз.

Результаты предыдущих работ. Ранее совместно с ООО «СТЦ» была спроектирована вычислительная реконфигурируемая платформа для высокопроизводительных вычислений и достигнуты соглашения об интеграции ее в СКЦ «Политехнический» [2]. Данная платформа выполнена в формате РСІех16 карты расширения, интегрирована в средства проектирования, предоставляемые производителем FPGA, и поддерживается в рамках стандарта OpenCL [5]. Каждый мо-

дуль содержит 4 FPGA Kintex UltraScale (XCKU115-2FLVA1517) фирмы Xilinx (каждая из которых имеет порядка 660 тыс. логических ячеек и 5,5 тыс. блоков умножениясложения), а также по 4 Гб DDR3 памяти

Для эффективного использования доступных вычислительных ресурсов и определения целесообразности применения аппаратно-реконфигурируемой платформы вместо традиционных массивов процессообщего назначения или CUDAускорителей для решения отдельно взятой задачи необходимы теоретические знания в области архитектуры реконфигурируемых вычислительных устройств и опыт практического использования средств разработки программного обеспечения. Для этого треучебно-лабораторного буется создание комплекса, в котором можно проводить подготовку и переобучение специалистов.

Себестоимость единицы разработанной платформы оценивается в 35 тыс. долл. США. Установка подобного оборудования является целесообразной для суперкомпьютерных центров и иного рода высокопроизводительных кластеров. Для задач обучения студентов, а также переподготовки специалистов подобные вычислительные мощности являются избыточными, а стоимость — слишком высокой для установки даже одной платформы в учебной лаборатории.

В связи с этим возникла потребность в создании аппаратно-реконфигурируемой платформы, представляющей собой полнофункциональное с точки зрения инструментария разработчика устройство, при этом имеющее достаточно низкую стоимость для использования в рамках учебного процесса.

Постановка задачи. В связи с отсутствием на рынке недорогих учебных платформ для реализации проектов, основанных на стандарте OpenCL, потребовалось исследовать возможность реализации реконфигурируемого вычислителя с поддержкой OpenCL на устройствах бюджетных линеек FPGA Xilinx, а в случае успеха — разработать и интегрировать в среду разработки SDAccel компании Xilinx бюджетный аппаратнореконфигурируемый вычислитель с под-

держкой стандарта OpenCL, предназначенный для массового использования в учебном процессе.

В процессе разработки были установлены следующие требования:

- формат карта расширения РСІе;

- логический ресурс FPGA достаточный для реализации интерфейсов взаимодействия с ПК и внешней памятью типа DDR3, а также для реализации вычислительных ядер;

- поддержка ПО платформа должна быть интегрирована в среду разработки, предоставляемую производителем FPGA, и поддерживаться средствами высокоуровневого синтеза, в частности, быть совместимой со стандартом OpenCL [5];

- стоимость производства не должна превышать 500 долл. США.

Для реализации поставленной задачи требуется:

- определить нижнюю границу количества доступных аппаратных ресурсов FPGA (таким образом формируется критерий выбора подходящей элементной базы: минимальная стоимость при достаточных ресурсах);

- определить необходимые для работы устройства периферийные элементы на плате;

• сравнить основные параметры.

Реализацию динамически-реконфигурируемых вычислителей обеспечивает технология частичной реконфигурации, позволяющая разделить конфигурационный файл на несколько независимых частей, каждая из которых отвечает за свою область на кристалле.

Данная технология применяется для того, чтобы часть логических ресурсов FPGA, реализующая PCIe-контроллер, оставалась неизменной, т. к. восстановление связи с отключившимся во время конфигурации устройством возможно восстановить только при перезагрузке системы; часть логических ресурсов FPGA, реализующая алгоритм, решающий требуемую задачу, реконфигурировалась в процессе решения прикладных задач; реализовать передачу конфигурации через PCIe-интерфейс, как наиболее быстрый способ.

Анализ минимальных требований к FPGA. Основываясь на опыте разработанной ранее платформы, были получены результаты по количеству занимаемых статической частью ресурсов. Они представлены в табл. 1. Помимо этого потребовалась поддержка аппаратных контроллеров PCIe и DDR3 памяти.

Таблица 1

Расход ресурсов FPGA для статической области для микросхемы XCKU115

Тable 1

FPGA resources utilization by static area of XCKU115 IC

| Тип ресурса | Использовано | Доступно | Использовано, % |

|-------------|--------------|----------|-----------------|

| LUT         | 84900        | 663360   | 13              |

| LUTRAM      | 11733        | 293760   | 4               |

| FF          | 120420       | 1326720  | 8               |

| BRAM        | 177          | 2160     | 8               |

| DSP         | 3            | 5520     | 0               |

| IO          | 128          | 624      | 21              |

| GT          | 8            | 48       | 17              |

| BUFG        | 20           | 1248     | 2               |

| MMCM        | 3            | 24       | 13              |

| PLL         | 4            | 48       | 8               |

| PCIe        | 1            | 6        | 17              |

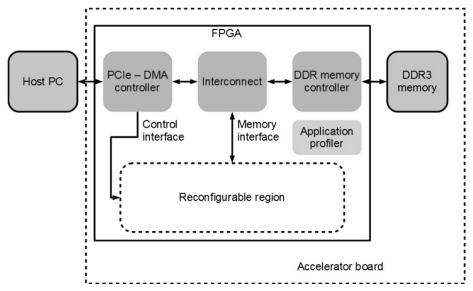

Рис. 1. Структура аппаратного проекта для FPGA Fig. 1. FPGA hardware project structure

Для создания бюджетной платформы предполагается использовать FPGA семейства Artix 7, имеющие достаточное количество логических ресурсов и относительно низкую стоимость. Для определения наименьшего необходимого количества аппаратных ресурсов, необходимых для реализации инфраструктуры OpenCL, проанализированы требования к отдельным его компонентам.

На рис. 1 представлена структура аппаратного проекта для FPGA, которую необходимо реализовать для возможности интеграции платформы в среду SDAccel [4].

Согласно технической документации, предоставляемой фирмой-производителем [4], произведена оценка ожидаемого количества ресурсов, занимаемого каждым из блоков. Для простоты приведено лишь количество логических ячеек (LUT) и триггеров (FF):

PCIe-DMA controller: 17066, FF – 17370; DDR3 controller: LUT – 14016, FF – 9019; Application profiler: LUT – 13413, FF – 14667;

Interconnect: LUT — 4320, FF — 1340. Итоговая оценка: LUT — 48815, FF — 42396.

Следует учесть, что при максимальной плотности расположения элементов логики возникает нехватка локальных соединительных трасс, в связи с чем трассировщик при компиляции использует трассы, лежащие вне области локализации логических ресурсов.

Поэтому требуется ввести коэффициент запаса 1,5-2, чтобы имелась возможность работы системы на более высоких частотах.

Исходя из представленных данных, сделаны следующие выводы: для реализации аппаратной поддержки OpenCl и интеграции платформы в среду SDAccel необходимо использовать FPGA, имеющую:

более 80 тыс. логических ячеек (LUT); более 80 тыс. триггеров (FF);

модули встроенной RAM памяти;

DSP-модули, реализующие операции типа multiply-accumulate (MAC);

аппаратный контроллер DDR3/4 памяти; аппаратный контроллер PCIe;

умножители частоты тактовых сигналов; блоки, обеспечивающие возможность частичной реконфигурации в процессе работы FPGA.

Обзор существующих решений. В табл. 2 приведены перечень и основные характеристики представленных на рынке платформ на базе FPGA фирмы Xilinx, конструктивно реализованных в формате PCIe, имеющих достаточное количество аппаратных ресурсов для реализации интерфейсов и вычислительных ядер OpenCL [4]. Несмотря на то, что использование нескольких FPGA позволяет реализовать полный потенциал шины PCIe [12], данный подход достаточно сложен в реализации, и все платформы, поставляемые фирмой Xilinx, имеют по одной FPGA на плате.

Таблица 2

### Некоторые из существующих аппаратных ускорителей

#### Table 2

### Some of existing hardware accelerator boards

| Платформа       | Семейство/Тип             | LUT    | DSP   | ,     | . 1 | Стоимость, |

|-----------------|---------------------------|--------|-------|-------|-----|------------|

|                 |                           |        |       | МБ    | Гб  | долл. США  |

| KCU105          | Kintex Ultrascale XCKU040 | 242 k  | 1920  | 21,1  | 2   | 2995       |

| AC701           | Artix7 XC7A200T           | 134 k  | 740   | 13    | 1   | 1295       |

| Alveo U200      | Virtex Ultrascale+XCVU9P  | 1182 k | 6840  | 345,9 | 16  | 8995       |

| Вычислитель СТЦ | Kintex Ultrascale XCKU115 | 2652 k | 22080 | 303,6 | 16  | 35000      |

Из таблицы видно, что существующие на рынке аппаратно-реконфигурируемые вычислители имеют большое количество доступных логических ресурсов и памяти для реализации вычислительных ядер. Это позволяет использовать данные платформы для построения высокопроизводительных гетерогенных вычислительных систем. Но из-за высокой стоимости они не подходят для массового использования в учебных лабораториях, обеспечивающих подготовку соответствующих специалистов.

Следует заметить, что для платформы AC701, в отличие от всех остальных, производитель не реализовал поддержку стандарта OpenCL.

Разработка пакета поддержки платформы. Согласно ранее сформированным требованиям для реализации устройства была выбрана микросхема типа XC7A200T, имеющая аппаратные контроллеры интерфейсов PCIe и DDR3, а также более 130 к логических ячеек [4].

Для интеграции разработанного аппаратно-реконфигурируемого вычислителя в среду разработки SDAccel компании Xilinx был создан пакет поддержки платформы, состоящий из аппаратной конфигурации для FPGA и программного обеспечения, поддерживающего взаимодействие хоста и вычислителя.

В табл. 3 представлено количество ресурсов микросхемы, занятых под аппаратный проект для FPGA, обеспечивающий взаимодействие хоста и вычислительного ядра, созданного в соответствии со стандартом OpenCL. Из данной таблицы видно, что количество использованных ресурсов имеет незначительные расхождения с теоретическими оценками.

Таблица 3

### Расход ресурсов FPGA для статической области микросхемы XC7A200T

Table 3

### FPGA resources utilization by static area of XC7A200T IC

| Тип<br>ресурса | Исполь-<br>зовано | Доступно | Исполь-<br>зовано, % |

|----------------|-------------------|----------|----------------------|

| LUT            | 49847             | 133800   | 37                   |

| LUTRAM         | 8488              | 46200    | 18                   |

| FF             | 59788             | 267600   | 22                   |

| BRAM           | 77                | 365      | 21                   |

| DSP            | 0                 | 740      | 0                    |

| IO             | 52                | 285      | 18                   |

| GT             | 1                 | 4        | 25                   |

| BUFG           | 13                | 32       | 40                   |

| MMCM           | 3                 | 10       | 30                   |

| PLL            | 2                 | 10       | 20                   |

| PCIe           | 1                 | 1        | 100                  |

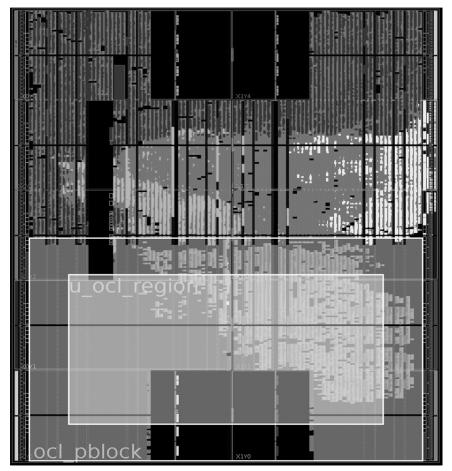

На FPGA выделена область, доступная для реконфигурации: где будет формироваться аппаратная структура, реализующая функциональность решаемой задачи. В связи с тем, что для создания реконфигурируемой области FPGA необходимо использовать прямоугольные зоны, наиболее подходящим вариантом выбрали разбиение кристалла, показанное рис. 2, где половина ресурсов FPGA выделена для реконфигурации, а вторая для ресурсов, обеспечивающих взаимодействие вычислителя с хостом и глобальной памятью.

Puc. 2. Результаты трассировки кристалла FPGA Fig. 2. FPGA routing results

На рисунке подсвеченный белым прямоугольник — область, доступная для реконфигурации и создания аппаратной структуры, реализующей функциональность решаемой задачи (Reconfigurable region). Остальные элементы в верхней половине микросхемы: PCIe-DMA controller; DDR memory controller; application profiler; interconnect.

Для интеграции разработанного аппаратно-реконфигурируемого вычислителя в среду разработки SDAccel необходимо сформировать:

файл конфигурации FPGA;

RTL-схему, описывающую статическую область;

драйвер взаимодействия хоста и вычислителя.

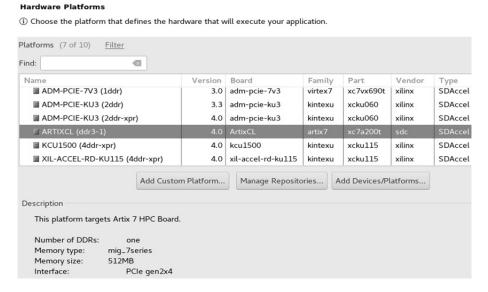

После формирования требуемой структуры папок и добавления платформы в среду разработки стало возможным использовать ее наряду с предустановленными платформами.

Результаты интеграции представлены на рис. 3. На рисунке показано меню выбора аппаратной платформы для проекта и информация о вычислителях. После формирования всех необходимых файлов и подключения их к среде SDAccel разработанный вычислитель появился в списке (под названием ARTIXCL).

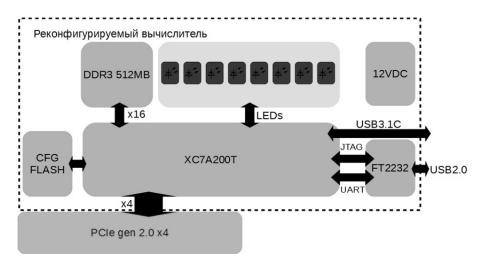

Проектирование аппаратной платформы. Основываясь на реализованном пакете поддержки платформы и общим требованиям к реализации устройств на базе FPGA, составлены требования к набору компонентов, устанавливаемых на плату, структура которой приведена на рис. 4, где изображены:

XC7A200T – FPGA компании Xilinx;

PCIe gen 2.0x4 — разъем PCIe для реализации протокола PCIe2.0x4;

DDR3 512 MB — DDR3 память объемом 512 MБ для реализации глобальной памяти — памяти, к которой имеют доступ как ядро, так и хост-компьютер;

Рис. 3. Список платформ, доступных для выбора в среде SDAccel Fig. 3. Available platforms list in SDAccel IDE

Рис. 4. Структура платы разработанного аппаратно-реконфигурируемого вычислителя Fig. 4. The designed hardware-reconfigurable accelerator structure

CFG FLASH — конфигурационная память для энергонезависимого хранения конфигурационных данных FPGA;

устройства ввода/вывода для обеспечения отладки: LEDS — 8 светодиодов; FT2232 — преобразователь USB-UART/USB-JTAG; USB3.1C — разъем типа USB3.1 type C для подключения внешних панелей управления; 12VDC — блок питания, на вход которого поступает 12 В.

По приведенному в табл. 4 списку можно дать приблизительную оценку сто-

имости каждого из представленных на схеме компонентов [13]. Затраты на проектирование, тестирование и прототипирование покрыты за счет полученного на разработку гранта от фонда М. Потанина и предоставленных компанией Xilinx лицензий, компонентов и отладочных комплектов.

По данным, приведенным в технической документации на выбранные компоненты, дана оценка максимальной мощности, потребляемой разработанным устройством: 8 Вт.

Таблица 4

Стоимость компонентов разработанного вычислителя

Тable 4

Hardware accelerator components' price

| Наименование              | Стоимость,<br>долл. США |

|---------------------------|-------------------------|

| Печатная плата (8 слоев)  | 15                      |

| FPGA (XC7A200T)           | 193                     |

| CFG FLASH (MT25QU256)     | 3,8                     |

| USB-UART (FT2232)         | 6,99                    |

| DDR3L (MT41K256M16TW-107) | 16,2                    |

| LED x8 (VLMO1500)         | 4,24                    |

| Блок питания (LTM4622x2)  | 32,7                    |

| Итого                     | 271,93                  |

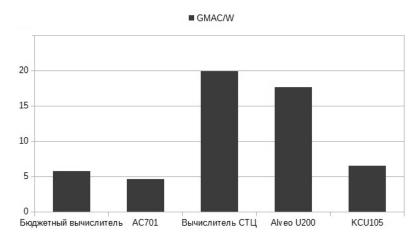

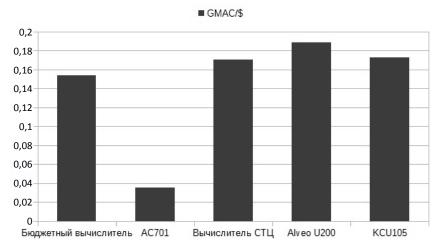

Для каждой платформы из табл. 2 составлена оценка максимальной потребляемой мощности, а также отношения производительности к мощности и производительности к стоимости. Результаты представлены на рис. 5 и 6.

Производительность оценивалась по количеству операций умножения с накоплением (MAC/Multiply-ассиmulate), выполняемых DSP-модулями. Потребляемая мощность для платы Alveo U200 взята из технической документации, для всех остальных — по результатам экспериментальных измерений.

Puc. 5. Отношение производительности к потребляемой мощности для вычислительных платформ Fig. 5. Performance to power consumption rate for listed hardware platforms

Puc. 6. Отношение производительности к стоимости для вычислительных платформ Fig. 6. Performance to price rate for listed hardware platforms

По представленным данным можно сделать вывод, что разработанная платформа превосходит платформу АС701, построенную на базе аналогичной FPGA по искомым критериям. Это связано с большей ценой и потребляемой мощностью, которые обусловлены наличием в платформе АС701 дополнительных периферийных устройств, не являющихся необходимыми для реализации OpenCL вычислителя, а также использованием в ней модульной SO-DIMM памяти. Кроме того, из графиков на рис. 5 и 6 видно, что разработанная платформа близка по свохарактеристикам платформе K КСU105, построенной на базе FPGA следующего поколения.

Заключение. На основе полученного ранее опыта разработки аппаратно-реконфигурируемых устройств и теоретических расчетов составлены требования к реализации платформы для нового учебно-лабораторного комплекса, обеспечивающего подготовку специалистов для работы с высокопроизводительными аппаратно-реконфигурируемыми системами.

Разработана бюджетная версия аппаратно-реконфигурируемого вычислителя с поддержкой стандарта OpenCL. Вычислитель интегрирован в средства разработки компании Xilinx и обеспечивает поддержку стандартной процедуры создания приложений для гетерогенных суперкомпьютерных систем.

В ходе сравнительного анализа существующих на рынке реконфигурируемых вычислителей показано, что разработанный бюджетный вычислитель не уступает своим более дорогим аналогам по критериям как отношения производительности на единицу стоимости, так и отношения производительности на единицу мощности.

На базе разработанного вычислителя планируется, в рамках проекта, поддержанного фондом М. Потанина, создание курса для программ магистратуры института ИКНТ (Санкт-Петербургский политехнический университет Петра Великого), обеспечивающего подготовку специалистов, имеющих знания, умения и навыки в технологии разработки и внедрения реконфигурируемых аппаратных ускорителей, адаптируемых в реальном времени вычислительного процесса под решаемую задачу.

Предлагаемый курс базируется на курсах, читаемых в рамках магистерской программы «Проектирование компьютерных систем», обеспечивающих знания в области аппаратных средств, архитектур современных вычислительных систем, системного и прикладного ПО, соответствующих инструментальных средств.

### СПИСОК ЛИТЕРАТУРЫ

- 1. **Каляев И.А., Левин И.И., Семерников Е.А., Шмойлов В.И.** Развитие отечественных многокристалльных реконфигурируемых вычислительных систем: от воздушного к жидкостному охлаждению // Труды СПИИРАН. 2017. Вып. 1. С. 27—39.

- 2. Заборовский В.С., Антонов А.П., Киселев И.О. Специализированные реконфигурируемые вычислители в сетецентрических суперкомпьютерных системах // Системы высокой доступности. 2018. Т. 14. № 3. С. 57—62.

- 3. Intel FPGA Devices // URL: https://www.intel.com/content/www/us/en/fpga/devices.html (Дата обращения: 04.09.2018).

- 4. Xilinx Inc. // URL: https://www.xilinx.com/ (Дата обращения: 04.09.2018).

- 5. OpenCL specification 1.2. // URL: https://www.khronos.org/registry/OpenCL/specs/opencl-1.2. pdf (Дата обращения: 04.09.2018).

- 6. **Awad M.** FPGA supercomputing platforms: A survey // 19th Internat. Conf. on Field Pro-

- grammable Logic and Applications. Praga, 2009. Pp. 564–568.

- 7. **Meeus W., Van Beeck K., Goedemé T., Meel J., Stroobandt D.** An overview of today's high-level synthesis tools // Design Automation for Embedded Systems. 2012. No. 16(3). Pp. 31–51.

- 8. Дордопуло А.И., Левин И.И., Каляев И.А., Гудков В.А., Гуленок А.А. Программирование вычислительных систем гибридного типа на основе метода редукции производительности // Параллельные вычислительные технологии: труды междунар. науч. конф. 2016. С. 131—140.

- 9. Shuhao Z., Bingsheng H., Wei Z. Melia a MapReduce framework on OpenCL based FPGA // IEEE Transactions on Parallel and Distributed Systems. 2015. Pp. 27–39.

- 10. **Kobayashi** R. OpenCL-ready high speed FPGA network for reconfigurable high perfor-

mance computing // Proc. of the Internat. Conf. on High Performance Computing in Asia-Pacific Region. 2018. Pp. 192–201.

11. Hill K., Craciun S., George A., Lam H. Comparative analysis of OpenCL vs. HDL with image-processing kernels on Stratix-V FPGA // 26th Internat. Conf. on Application-Specific Sys-

tems, Architectures and Processors. IEEE, 2015. Pp. 189–193.

- 12. **Gao S.** Characterization of OpenCL on a scalable FPGA architecture // 2014 Internat. Conf. on Reconfigurable Computing and FPGAs. 2014. 8 p.

- 13. Digi-key Electronics // URL: https://www.dig ikey.com/ (Дата обращения: 27.10.2018).

Статья поступила в редакцию 10.10.2018.

#### REFERENCES

- 1. **Kalyayev I.A., Levin I.I., Semernikov Ye.A., Shmoylov V.I.** Evolution of domestic multichip reconfigurable computer systems: from air to liquid cooling. *Trudy SPIIRAN*, 2017, Vol. 1, Pp. 27–39. (rus)

- 2. **Zaborovskiy V.S., Antonov A.P., Kiselev I.O.** The reconfigurable computational modules in network-centric supercomputer systems. *Sistemy vysokoy dostupnosti*, 2018, Vol. 14, No. 3, Pp. 57–62 (Accessed: 04.09.2018). (rus)

- 3. Intel FPGA Devices. Available: https://www.intel.com/content/www/us/en/fpga/devices.html (Accessed: 04.09.2018).

- 4. Xilinx Inc. Available: https://www.xilinx.com/(Accessed: 04.09.2018).

- 5. OpenCL specification 1.2. Available: https://www.khronos.org/registry/OpenCL/specs/opencl-1.2.pdf (Accessed: 04.09.2018).

- 6. **Awad M.** FPGA supercomputing platforms: A survey. *19th International Conference on Field Programmable Logic and Applications*, Praga, 2009, Pp. 564–568.

- 7. Meeus W., Van Beeck K., Goedemé T., Meel J., Stroobandt D. An overview of today's high-level synthesis tools. *Design Automation for Embedded Systems*, 2012, No. 16(3), Pp. 31–51.

- 8. **Dordopulo A.I.**, **Levin I.I.**, **Kalyayev I.A.**, **Gudkov V.A.**, **Gulenok A.A.** Programming of hybrid computer systems based on the performance reduction method. *Parallelnyye vychislitelnyye tekhnologii: trudy mezhdunarodnoy nauchnoy konferentsii*, 2016, Pp. 131–140. (rus)

- 9. **Shuhao Z., Bingsheng H., Wei Z.** Melia a MapReduce framework on OpenCL based FPGA. *IEEE Transactions on Parallel and Distributed Systems*, 2015, Pp. 27–39

- 10. **Kobayashi R.** OpenCL-ready high speed FPGA network for reconfigurable high performance computing. *Proceedings of the International Conference on High Performance Computing in Asia-Pacific Region*, 2018, Pp. 192–201.

- 11. Hill K., Craciun S., George A., Lam H. Comparative analysis of OpenCL vs. HDL with image-processing kernels on Stratix-V FPGA. 2015 IEEE 26th International Conference on Application-Specific Systems, Architectures and Processors, Pp. 189–193.

- 12. **Gao S.** Characterization of OpenCL on a scalable FPGA architecture. *2014 International Conference on Reconfigurable Computing and FPGAs*, 2014, 8 p.

- 13. Digi-key Electronics. Available: https://www.digikey.com/ (Accessed: 27.10.2018).

Received 10.10.2018.

### СВЕДЕНИЯ ОБ ABTOPAX / THE AUTHORS

AHTOHOB Александр Петрович ANTONOV Alexander P.

E-mail: antonov@eda-lab.ftk.spbstu.ru

ФИЛИППОВ Алексей Семенович FILIPPOV Alexey S.

E-mail: alexey.s.filippov@gmail.com

КИСЕЛЕВ Иван Олегович KISELEV Ivan O.

E-mail: kio.93@mail.ru